## Transmitting SXGA Video Signal through 1kft (300m) CAT-5 Cable

Application Note

January 2, 2008

AN1318.0

#### Introduction

With the world dominance of personal computer systems, demand for long distance component video transmission is increasing at an unprecedented pace. The applications areas of greatest demand are KVM systems, server farms, information message boards and educational classrooms. This application note provides in-depth information on some of the most important physical support technologies and constraints; CAT-5 cable characteristics, SXGA video standards and video amplifier/line drivers and receiver bandwidth and slew rate requirements. The trade-offs of differential line driver and receiver topologies are discussed in detail. This application note also presents termination techniques and video equalization strategies. Further design issues involving power supply schemes and video timing transmissions are also also described.

The goal of this application note is to present the most current design methods for transmitting high bandwidth SXGA video signal over long distances of CAT-5 cable (300m or more). The enormous cost benefits of CAT-5 cable will also be discussed; for instance, the average cost of a 100m of CAT-5 cable is \$20 while the average cost of a 100m of Coax Cable could easily exceed \$240. Furthermore, wiring is reduced from a bulky hard to manage bundle of 3 cables to 1 easily pulled cable. Additionally, CAT-5 cable has a 4th twisted pair available, which can be used for KVM signal, audio, timing or control signal transmission.

#### SXGA Video Standard

Table 1 presents key parameters of 76Hz SXGA video signal.

The signal bandwidth comes from Equation 1:

$BWS = 1/2[(K \bullet AR \bullet (VLT)^{2} \bullet FR) \bullet (KH/KV)] = 51.9MHz$ (EQ. 1)

Where:

BWS = Signal bandwidth, K = Kell factor

Visual information is lost due to the probability that some of the video information will be displayed during the retrace rather than the active portion of the scan line. Assuming 30% of the visual information is loss, we have K = 0.7.

AR = Aspect ratio (the display width divided by display height) =1.33

VLT = Total number of vertical pixels = 1067

FR = Frame rate or refresh rate = 76

KH = Ratio of total horizontal pixels to active pixels, which equals 1720/1280 = 1.34

KV = Ratio of total vertical lines to active lines = 1.04

#### TABLE 1. KEY PARAMETERS OF 76Hz SXGA VIDEO SIGNAL

Authors: Mike Wong, Sameer Vuyyuru and Marvin Li

| PARAMETER                    | VALUE |

|------------------------------|-------|

| Active Horizontal Pixels     | 1280  |

| Active Vertical Pixels       | 1311  |

| Total Horizontal Pixels      | 1720  |

| Total Vertical Pixels (VLT)  | 1067  |

| Frame Rate (FR) (Hz)         | 76    |

| Horizontal Rate (KHz)        | 81.1  |

| Pixel Rate (Mpixels/second)  | 139.5 |

| Signal Bandwidth (BWS) (MHz) | 51.9  |

# Amplifier Bandwidth and Slew Rate Requirements

To maintain video signal integrity, we need to maintain 0.1dB bandwidth to the signal bandwidth (BWS). When selecting amplifiers, special attention should be given to its frequency response characteristics; for instance, for a signal pole amplifier the 3dB bandwidth required to handle 51.9MHz is 6.5\*51.9MHz = 337MHz. For multiple pole amplifiers (most modern high speed amplifiers are multiple pole amplifiers), the 3dB bandwidth should be set to 3 times the signal bandwidth, which for the previous example would be 155.7MHz. The slew-rate can be calculated from the signal amplitude and pixel rate. Therefore to maintain video signal integrity with a pixel rate of 139.5MHz while allowing the signal to complete its transition during ¼ of a clock period, use Equation 2:.

Slew Rate =

$$\frac{1}{\left(\frac{1}{4} \times \text{Pixel Time}\right)} = \frac{1}{\left(\frac{1}{4} \times \frac{1}{139.5\text{MHz}}\right)} = 558 \text{V}/\mu\text{s}$$

(EQ. 2)

VESA DMT standards also define 60Hz refresh rates and 80Hz refresh rates but the most common usage is the 76Hz refresh rate.

### CAT-5 Cable Characteristics

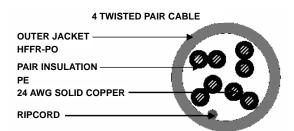

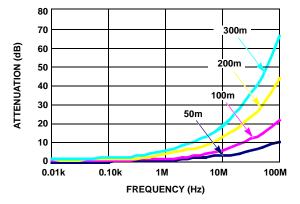

Figure 1 shows the cross section of Standard CAT-5 cable consisting of 4 twisted pairs of AWG 24 cable, which has a characteristic impedance of  $100\Omega$ . The DC resistance is  $10\Omega/100$ m with a capacitance 4.6nF/100m. One important characteristic of SXGA video transmission is high frequency cable attenuation, which increases exponentially over frequency and distance. Figure 2 shows the effects of signal frequency and cable length on the signal attenuation. The relationship between cable attenuation, signal frequency and cable length of 3:

$$Atten(F, L): L \cdot \left(1.967 \cdot \sqrt{F} + 0.023 \cdot F + \frac{0.05}{\sqrt{F}}\right)$$

(EQ. 3)

L is cable distance in 100m and F is the signal frequency.

FIGURE 1. CAT-5 CABLE CROSS SECTION

FIGURE 2. CAT-5 CABLE ATTENUATION CHARACTERISTICS

FIGURE 3. CAT-5 CABLE CROSS SECTION

#### **Differential Line Driver Topologies**

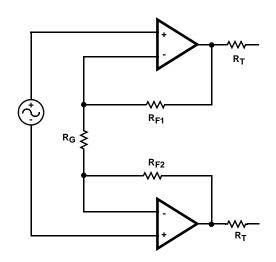

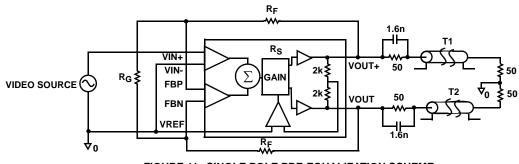

Figure 3 illustrates a standard differential input and output line driver system built with discrete operational amplifiers. The differential output driver doubles the output voltage swing - while the resistors  $R_F$  and  $R_G$  determine the circuit voltage gain with Equation 4:

$$\frac{V_{OUT}}{V_{IN}} = 1 + 2* \frac{R_F}{R_G}$$

(EQ. 4)

High noise rejection, such as 60Hz power line interference, is accomplished by amplifying only the differential input voltage signals and not amplifying the common mode input voltage.

The only real disadvantage of this circuit is the required differential input signal sources.

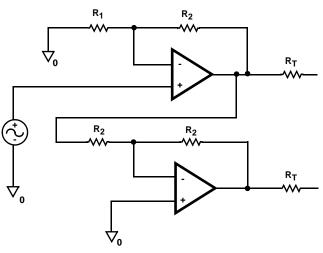

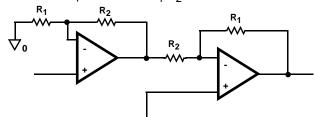

Typically, signals originate in single ended rather than differential form. Converting a single ended signal to differential mode prior to line transmission reaps the benefits of high common mode noise reduction. The circuit in Figure 4 provides a very simple way to generate a differential output signal from a single ended input signal using two operational amplifiers; the upper amplifier is non-inverting while the bottom is inverting. Note the amplifiers have different feedback ratios (close loop gain) that results in different bandwidths for voltage feedback amplifiers. The difference in bandwidth causes higher frequency signal mismatch and can lead to higher distortion. For current feedback amplifiers, the bandwidth stays relatively constant at different gain settings. Since the bandwidth is primarily a function of the value of the feedback resistors, one should keep the feedback resistor the same for current feedback amplifiers.

FIGURE 4. SINGLE-ENDED TO DIFFERENTIAL LINE DRIVER

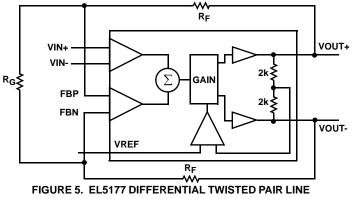

Figure 5 illustrates the complete block diagram of the EL5177, a 550MHz single/differential input to differential output amplifier, which can be used as a single ended to differential converter. This device is internally compensated for a closed loop gain of +1 stable; the gain is set by R<sub>F</sub> and R<sub>G</sub>. V<sub>ODM</sub> is the output in differential mode and V<sub>OCM</sub> is the common mode output voltage.

The voltage applied at the VREF pin sets the output common mode voltage.

DRIVER BLOCK DIAGRAM

#### **Differential Line Receiver Topologies**

Figure 6 shows a differential to single ended converter implemented with high speed amplifiers. This circuit receives a differential voltage, reduces the common mode input gain to zero and terminates in a single ended output. The advantage is both a very high input impedance and very high common mode rejection achieved with simplicity. Bandwidth mismatch of the two amplifiers introduces the possibility of high frequency distortion. Furthermore, high output swing is required to achieve good common mode rejection. The differential gain is determined by R<sub>1</sub> and R<sub>2</sub> resistors with the relationship: Gain =  $1 + R_1/R_2$ .

FIGURE 6. DIFFERENTIAL TO SINGLE-ENDED CONVERTER

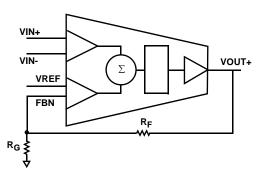

Figure 7 shows the complete block diagram of the EL5175, a 550MHz differential input to single ended output amplifier, which can be used as a differential to single ended converter. This device is internally compensated for closed loop gain of +1 stable and the gain is set by  $R_F$  and  $R_G$ . The output voltage is equal to the difference of the inputs plus  $V_{REF}$  and then multiplied by the gain.

$$V_{ODM} = (V_{IN+} - V_{IN-} + V_{REF})^* (1 + (R_F / R_G))$$

(EQ. 6)

FIGURE 7. EL5175 DIFFERENTIAL TO SINGLE-ENDED AMPLIFIER BLOCK DIAGRAM

#### **Termination Techniques**

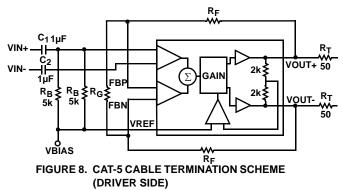

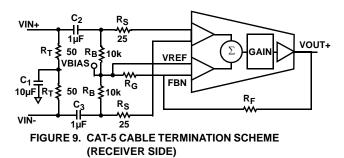

To avoid reflections and maintain integrity of the input video signals, the line driver output must be properly terminated. The characteristic impedance of a standard CAT-5 cable is  $100\Omega$ which is split into two  $50\Omega$  resistors for driving the line differentially. Figures 8 and 9 show the termination scheme on the driver and receiver sides. C1 and RT of the receiver form a low pass filter to reject high frequency common noise picked-up by the cable. C<sub>2</sub> is used to isolate the DC voltage difference caused by grounding inequalities between the driver and receiver systems. RB sets up the bias voltage for the receiving amplifiers. The BW of the high pass filter formed by R<sub>B</sub> and C<sub>2</sub> must be low enough to pass all the video signals. For SXGA video signals, the low pass band must be less than 20Hz. A small resistor R<sub>S</sub> is placed to isolate the input capacitance of the receiver from the PCB trace inductance to avoid LC resonance effect at the receiving amplifier inputs.

Some video systems do not have a negative supply available and require single supply operation. Figure 9 shows a simple implementation of single supply operation. The video signal is AC coupled into the driver inputs and the input DC bias is setup by  $R_1$  and  $R_2$  resistors from a bias voltage. The output is centered around the bias voltage, which should be set to  $\frac{1}{2}$  the supply voltage. AC coupling may be needed to avoid a DC voltage presence on the line. At the receiver, the incoming video signal is first terminated into two  $50\Omega$  resistors. The center tap of these resistors is AC coupled to ground to eliminate high frequency common mode noise pickup by the cable. The signal is once again AC coupled into the input in the same fashion as the single supply differential line driver.

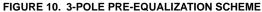

#### Video Equalization Strategies Pre-equalization vs Post-equalization

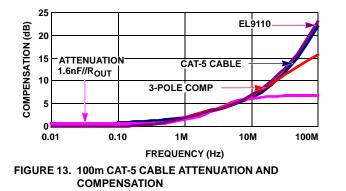

Figure 11 shows a very simple method of pre-equalizing the line with the inclusion of a parallel 1.6nF capacitor with the termination resistor. The 1.6nF capacitor shorts out the 50 $\Omega$  termination resistor at high frequencies and allows a larger amount of high frequency signal on the line. The 1.6nF capacitor in parallel with 50 $\Omega$  termination resistor is a single pole high pass filter with 3dB zero at 2MHz. The maximum achievable gain at high frequency is limited to 6dB because the termination resistor is shorted and all the signal is realized on the line. In this scheme, cable parasitic capacitance appears at the amplifier output and can lead to oscillation.

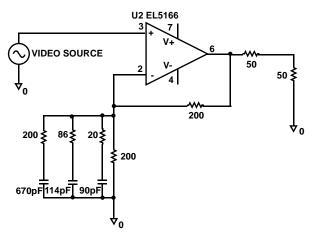

Figure 10 shows a 3-pole compensation circuit using a 1GHz bandwidth high slew rate amplifier. The circuit is configured around the gain setting resistor that sets the poles at 1.2MHz, 15MHz and 100MHz respectively. The amount of high frequency compensation is determined by the gain setting resistor. The capacitor and resistor combinations set the pole frequencies. Theoretically, this circuit can be used for both pre-equalization and postequalization. In practice, the line driver slew rate and output swing limit the pre-equalization performance; for instance, a 1V, 60MHz input signal becomes a 12.6V, 60MHz signal at the line driver output, requiring an approximately 5kV/us slew rate. The slew rate of the EL5166 is 5.5kV/µs with a maximum supply voltage of 12V and its maximum output swing is 8V. Most modern high speed amplifiers are built on less than 12V processes. This circuit should always be implemented in a post-equalization configuration where the incoming high frequency signal is low in amplitude.

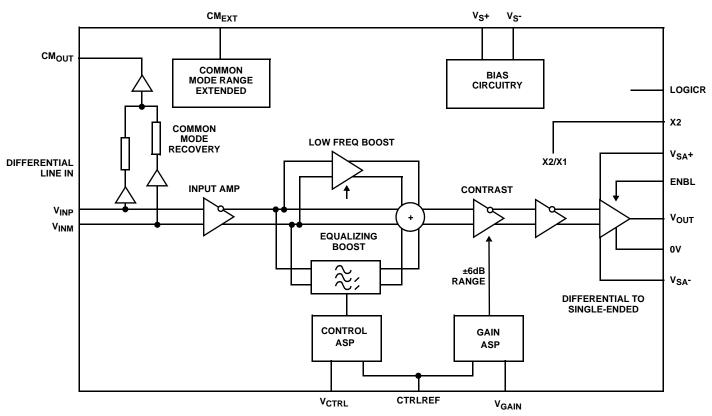

Figure 12 shows a simplified block diagram of the EL9110, a differential line receiver with an integrated CAT-5 cable compensation network. The differential input signal is used to recover the common mode input signal, which after recovery is amplified and buffered to the output at CMOUT. The differential input signal is buffered to drive the LOW FREQ BOOST amplifier. The high frequency components are processed in a proprietary EQUALIZING BOOST amplifier while the frequency response of this amplifier is voltage-controllable and matches cable losses. The control voltage input is the high frequency gain boost control, CTRLREF is the reference for the control voltage. The differential signals are summed and amplified further by the variable gain (CONTRAST) amplifier. The signal level adjustment is accomplished by switching the gain with a digital control X2- of the following amplifier " X2/X1". The logic input has its own reference LOGICREF. Finally, the differential signal is converted to a single ended signal and comes out of the VOUT pin. The output signal is referenced to the 0V input pin. For power economy, the entire chip can be turned off with the ENBL pin.

FIGURE 11. SINGLE POLE PRE-EQUALIZATION SCHEME

FIGURE 12. EL9110 DIFFERENTIAL LINE RECEIVER WITH CAT-5 CABLE COMPENSATION

Figure 13 shows 100m CAT-5 cable attenuations characteristics and the frequency responses of the 3 cable compensation circuits. The  $1.6pF//R_{OUT}$  compensation circuit works well up to 10MHz. The frequency response of the 3-pole compensation circuit comes very close to matching the CAT-5 cable attenuation. EL9110 V<sub>GAIN</sub> is set to 0.24V for 100m CAT-5 cable, the EL9110 compensates perfectly for signal frequencies up to 100MHz.

### Video Sync/Timing Transmission

As described earlier, the standard SXGA video consists of 5 signals; RGB video signals, vertical and horizontal sync signals. Standard CAT-5 cable has 4 pairs of twisted wires. To pass all 5 SXGA signals, one can encode the vertical and horizontal signs into a composite sync signal by using the Super Sync Separator EL4511. The composite video signal can then be transmitted through the fourth twisted wire pair of CAT-5 cable. The EL1883 can be used on the receive side to separate horizontal and vertical sync signals from composite sync input signals.

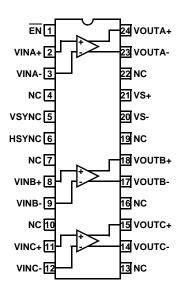

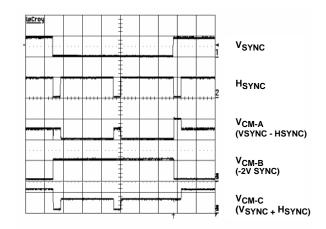

In cases where the fourth twisted wire pair is not available because it is being used to pass KVM or other signals, the EL4543 is capable of encoding the  $H_{SYNC}$  and  $V_{SYNC}$  on the common mode of the video signal. The EL4543 block diagram is shown in Figure 14. The  $V_{SYNC}$  and  $H_{SYNC}$ inputs and the common mode outputs of the EL4543 are shown in Figure 15. The relationship between  $H_{SYNC}$ ,  $V_{SYNC}$  and the Common Mode Outputs is shown in Equations 7, 8 and 9:

| $V_{cm-A} = V_{SYNC} - H_{SYNC}$ | (EQ. 7) |

|----------------------------------|---------|

|----------------------------------|---------|

$$V_{cm-b} = -2^* V_{SYNC}$$

(EQ. 8)

$$V_{cm-c} = V_{SYNC} + H_{SYNC}$$

(EQ. 9)

It is clearly shown that the sum of the common mode voltages results in some finite DC level with no AC content. This eliminates EMI radiation into any common mode signal along the CAT-5 cable.  $H_{SYNC}$  and  $V_{SYNC}$  can be regenerated from the voltage differences in the common mode voltages.

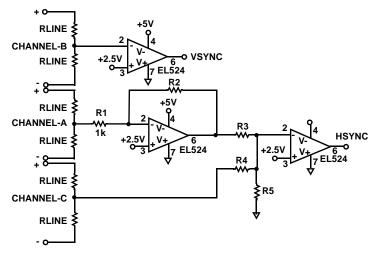

The circuit in Figure 16 accepts and decodes Common Mode signals to regenerate  $H_{SYNC}$  and  $V_{SYNC}$  waveforms at their respective outputs. The Common Mode Channel-B signal is passed through an inverting comparator and level shifted 2.5V to generate  $V_{SYNC}$ . The Common Mode Channel-A signal is level shifted, inverted and summed with a level shifted Channel-C signal to generate  $H_{SYNC}$ .

FIGURE 14. EL4543 TRIPLE DIFFERENTIAL LINE DRIVER WITH H<sub>SYNC</sub> AND V<sub>SYNC</sub> ENCODER

FIGURE 15. EL4543 TEST RESULTS

FIGURE 16. EL4543 SYNC ENCODER

Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that the Application Note or Technical Brief is current before proceeding.

For information regarding Intersil Corporation and its products, see www.intersil.com